## Teaching Computer Architecture using a Collaborative Approach: The SIENA Tool, Tutorial Sessions and Problem Solving\*

LORENZO MORENO, CARINA GONZÁLEZ, EVELIO J. GONZÁLEZ, BEATRICE POPESCU and CLAUDIA O. L. GROENWALD<sup>1</sup>

Departments of Systems Engineering and Automation, and Computer Technology and Architecture, Av. Astrofísico Fco. Sánchez S/N, CP 38206, Universidad de La Laguna, Tenerife, Spain

<sup>1</sup> Faculty of Mathematics. Postgraduate course *The Teaching of Sciences and Mathematics*, Universidade Luterana do Brasil, Brazil. E-mail: ejgonzal@ull.es

This paper presents a teaching–learning methodology that combines Blended Learning (BL) and Computer-Supported Learning (CSCL). We have created a tool called SIENA that assists students with self-learning. The SIENA tool uses conceptual maps and adaptive testing to guide the learning process of students working together in small groups. The tests, which include functions that are specifically suited to online collaborative work, use teaching–learning materials and questions that have been developed in collaboration with final-year students taking the subject Computer Architecture.

Keywords: higher education; blended learning; continuous assessment; collaborative learning; adaptive tests

## 1. Introduction

The European Union (EU) recently established the European Higher Education Area. With this move, the EU wants to ensure that all higher education programs across Europe are on an equal footing, thus improving student mobility and employability, lifelong learning opportunities, and also the competitiveness and quality of universities in the EU. What this actually means is that all European universities now find themselves facing the challenging questions of how to develop more transparent study programs, and how to improve the quality of their own programs. This context provided us with the opportunity to question whether any adaptations or improvements could be made to how we were delivering different subjects to our own students.

What was clear from the start was that we wanted to provide a methodology and tool that could help teachers to perform continual assessment: we believe that it allows teachers to evaluate their students' understanding and abilities better than does a single final exam, and that students also learn better if they are given the opportunity to retake failed tests. The only problem with continuous assessment is that it is often based on subjective reasoning, rather than on the use of objective data, so we would also need to overcome this limitation.

We identified that we should be trying to provide a tool that: a) facilitates the assimilation of concepts by students, b) increases motivation amongst students, c) allows teaching staff to monitor and access student performance and participation, and d) improves the objectivity of information available to teaching staff regarding their students' performance and participation. With this last point, we want to ensure that the continuous assessment process is made more objective, and thus ensure that the quality of the course can be reproduced year after year, or at other EU universities. Based on these ideas, we propose incorporating new technologies in the classroom and combining them with innovative teaching methods to improve the teaching-learning process. This paper presents our proposed methodology and our conclusions regarding its performance.

Our proposed methodology focuses primarily on the use of Blended Learning, which consists of simultaneously delivering both classroom-based activities and distance learning and self-evaluation on the part of the student. However, it is worth noting that BL also includes a strong collaborative aspect, as will be seen later on. For the purposes of our research we have designed a tool for our students to use when working together in small groups. This tool has been designed for autonomous learning and to guide the learning process through the use of conceptual maps and adaptive tests. It also provides the teacher with personalised information on each student's progress. The adaptive tests include functions specifically suited to online collaborative work. The tool is called SIENA.

We tested our methodology on students studying Computer Architecture. This subject is one of the last subjects to be offered as part of our Computer Engineering course. As these were final-year students they demonstrated an intellectual maturity (having completed Computer Structures, Operating Systems, Network Switches, etc.), which made it possible for us to evaluate and refine our tool and materials by collaborating with them on the following:

- Content creation and content searches

- The creation of questions that are then incorporated into the adaptive tests that are used during self-evaluation (details of which are presented further on)

- The validation of different tools such as simulators and SIENA.

Section 2 of this paper contains details of the fundamental basics of our methodology and its key pedagogical aspects. Section 3 provides an overview of the Computer Architecture course and its modules. Section 4 contains the methodology used and details of the SIENA tool—how SIENA was developed, how it is used for group learning, how it is used for continuous assessment, how simulators can be used for problem solving—and we present details of the experiment carried out. In the final sections, we present an analysis of the results of our experiment and present feedback from both staff and students regarding their experiences of using our methodology. Lastly, we present our final conclusions.

# 2. Overview of BL and CSCL methodology

The Blended Learning (BL) approach is a teaching and learning strategy that has been successfully applied across a range of different situations [1]. Table 1 illustrates the advantages (reinforced in the BL approach) and disadvantages (mitigated by the BL approach) of face-to-face learning and distance learning [2–10].

We use Computer-Supported Collaborative Learning (CSCL) to complement the BL approach. The use of CSCL can facilitate group learning. It can also facilitate learning in which the communication process is produced bi-directionally between people with different roles, i.e. professors and students [10]. This kind of collaborative strategy requires more social interaction and student participation than traditional methods. However, it has been demonstrated that the collaborative effort involved during the learning process results in a more thorough assimilation of concepts and better knowledge building [11]. These strategies depend on a student-centred learning process [10]. For this to work, it is essential that teachers are still able to monitor, assess, and assist students whilst they work individually or in groups [10-16].

One of the key aspects of our proposal is to increase student motivation. We aim to achieve this in four ways [17–24]:

- by increasing student self-esteem and autonomy. traditional strategies tend to be based solely on the binary 'reward/punishment', which is more focused on the results of an assessment than on the learning process itself [25];

- by avoiding repetitive activity patterns in class;

- by making the student aware that his/her learning requirements are connected to the educational environment;

- by designing online activities using systems that

|                       | Advantages                                                                                                                                                                                                                                                                                                                                    | Disadvantages                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Face-to-face learning | Sense of belonging to a group, which in turn<br>serves to encourage confidence felt towards<br>teaching staff                                                                                                                                                                                                                                 | Not all students are able to participate, especially<br>when there are more dominant personalities in the<br>classroom                                                                                                                                                                                                                                       |  |  |

|                       | Quick creation of inter-connected ideas. Quick discoveries through guessing                                                                                                                                                                                                                                                                   | Time limitations: it is not always possible to go in<br>as much detail as is desired during debates for fear o                                                                                                                                                                                                                                               |  |  |

|                       | It is possible to carry out more complex tasks                                                                                                                                                                                                                                                                                                | running out to time                                                                                                                                                                                                                                                                                                                                          |  |  |

| Distance learning     | Enables cooperative and collaborative learning<br>Improves active participation<br>Participation does not depend on the<br>surroundings or on timeframes<br>Low cost<br>The student is able to dedicate more time to the<br>activity if necessary<br>Exams and exercises can be done online<br>Flexibility in completing the subject syllabus | Poor in terms of social communication<br>(self-study, this method is considered impersonal<br>)<br>Initial set up requires time and effort<br>Access may be affected due to possible<br>log-in problems<br>Launching it may require a multidisciplinary team<br>Limits the development of associations via idea<br>strings, or of discovery through guessing |  |  |

|                       | r textointy in completing the subject synabus                                                                                                                                                                                                                                                                                                 | Tendency towards producing excess content<br>Higher student dropout rates are more likely<br>Possible tendency towards apathy and the<br>postponement of activities                                                                                                                                                                                          |  |  |

Table 1. Advantages and disadvantages of face-to-face learning and distance learning (adapted from [8])

| Units                                                                         | Subject                                                                                                    | Topics                                                                                                                                                                                                                |  |  |  |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Introduction                                                                  | Design fundamentals.                                                                                       | Performance measurements. Design of instruction repertoires:<br>Microcontrollers, Embedded systems, Digital signal processors<br>General-purpose processors                                                           |  |  |  |

| Techniques for increasing performance I                                       | Processor segmentation.                                                                                    | Type of dependencies. Anticipation technique. Exceptions.<br>Delayed jump. Segmentation of operational units.<br>Simulators.                                                                                          |  |  |  |

|                                                                               | Vector processors.                                                                                         | Operational units. Load unit/storage unit. Compilation techniques.<br>Simulators.                                                                                                                                     |  |  |  |

| Techniques for increasing<br>performance II: dynamic and<br>static approaches | Instruction Level Parallelism (ILP).                                                                       | Superscalars: Tomasulo algorithm. Dynamic control of branches<br>Types. VLIW/EPIC processors: Predicate registers, Compilation<br>techniques.<br>Simulators.                                                          |  |  |  |

| Thread level parallelism                                                      | Multi-threading and<br>Simultaneous multi-threading.                                                       | Characteristics: Fine grained and coarse grained. Example architecture: Niagara, Montecito                                                                                                                            |  |  |  |

| Memory hierarchy                                                              | Virtual memory and cache.                                                                                  | Types. Page tables. Organisations. Top down/Bottom up traversa<br>of page tables. TLB. Replacement algorithms. Cache memory<br>organisation. Techniques for improving cache performance.<br>Coherence.<br>Simulators. |  |  |  |

| Interconnection networks                                                      | Basic definitions. Organisational<br>structure.<br>Direct networks.<br>Indirect networks.<br>System buses. | Bandwidth and latency. Network .switch. Classification of<br>interconnection networks.<br>Characterization. Topologies.<br>Characterization. Topologies.<br>Hyper-transport.                                          |  |  |  |

| Multi-processor Architecture                                                  | Multicore, Manycores, Shared<br>Memory, Scalable multi-<br>processor.                                      | Coherence: Snooping, directory. Synchronization.<br>Graphics and computing GPUs.                                                                                                                                      |  |  |  |

Table 2. Course syllabus-main units, subjects and topics of Computer Architecture

do not merely transfer the classroom-based activities into a virtual format.

## 3. Computer architecture: an overview

We felt that this subject was ideal for testing our methodology because simulators are often used in this subject. Students create these simulators as part of their final thesis [26–28]. These simulations are designed to improve the understanding of complex problems. In Table 2 we provide details of the course. It is from this content that we create the conceptual maps that are used in adaptive testing.

## 4. Methodology

Students are told to organise themselves into groups (with a maximum of 2 or 3 students per group). Students are instructed to work on course content: they must use the information provided to them by their teacher, i.e. theoretical notes, practical exercises carried out on simulators, proposed exercises, and extra reading materials (books, magazines, websites, etc.).

Students are also instructed to a tool called SIENA that is designed to assist them with selfstudy and self-evaluation. This tool also allows teaching staff to personalise tutorial sessions. It provides objective data on student participation and performance that can be used by the teacher to provide accurate feedback and an objective grading system for continuous assessment.

Students may be asked to work individually, or collaboratively—this could be within their group, or each group may be required to work with the other groups. SIENA is able to monitor an individual student's work, whether it is produced alone or during collaborative tasks.

In the following sub-sections, we discuss each of the elements of our proposed methodology in detail.

## 4.1 The SIENA tool

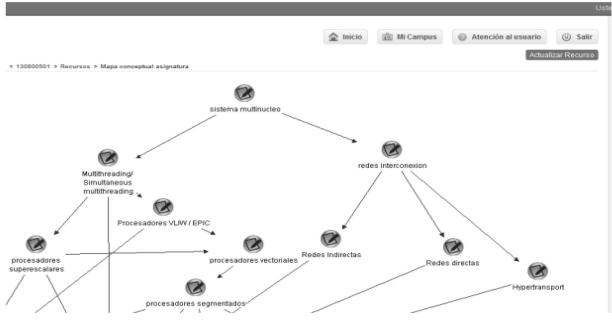

The Integrated Teaching-Learning System (SIENA) has been created to help students with self-study and self-evaluation [29-30]. SIENA must be used together with a tool called Compendium. We use the Compendium tool to create a conceptual map of the subject, Computer Architecture. Once created, we open SIENA and import the map from Compendium. This conceptual map is based entirely on a relationship of knowledge: the nodes on the map are the topics of the subject, and the connection between these nodes is such that if topic B connects to topic A, then to understand B correctly a student must first understand A.

Fig. 1. Example of a conceptual map designed using Compendium (detail).

To illustrate this we have provided a conceptual map from the subject in Fig. 1. The nodes of this subject are the *topics* that make up the subject. These nodes are connected through a relationship of knowledge; for example, if a student wants to start to study *Multicore Systems*, the student must first have understood the nodes *Interconnection Networks* and *Multi-threading Systems andSimultaneous Multi-threading*.

The SIENA tool includes an adaptive test containing multiple-choice questions for each of the nodes on the conceptual map (this is in addition to the node content). These tests have been implemented using Bayesian networks [31]. These networks connect the concepts of the map to the questions. This allows the adaptive test to estimate a student's knowledge, which it does by using the answers that students give to each of the subsequent questions presented by the tool.

SIENA works by:

- Selecting the 'target node': Students follows the self-study content and complete the tests presented for each node by the SIENA tool until they reach the target node. The target node is the node that the student should reach by correctly applying previous knowledge. If the students have not assimilated enough knowledge to pass a specific node then the tool will prevent students progressing further. However, the tool does allow students to explore alternative routes by presenting them with alternative nodes if this happens.

- *Calculating understanding*: When a student answers a question on any given node, the adaptive test uses Bayes formula to calculate a stu-

dent's posterior knowledge. This formula uses three parameters: the student's a priori knowledge, difficulty (probability of correctly answering the question supposing that the idea is understood), and guessing (probability of correctly answering the question supposing that the idea is not known).

• Selecting a new question: The next question, which is selected from all the remaining questions associated with the node, is chosen to maximize an objective function.

The test ends if the difference between the estimated knowledge is no greater than 0.01 for the last five questions, or there are no more questions.

Figure 2 shows the data for a question with all of its parameters, and Table 3 contains an example of the test results that are visible to both the professor and to the group of students.

## 4.1.1 How the test questions were developed

The conceptual map produced for Computer Architecture consists of fifteen nodes and holds approximately 1500 questions. The academic staff worked in collaboration with the final-year students to select the topics and content used in SIENA. The questions themselves were written by the students and refined with feedback from the academic staff. The process of constructing and validating the entire volume of questions has taken three academic years.

Our students needed to make significant efforts with regards to their own learning in order to prepare the questions for each node of the conceptual map. To assist their efforts, the teachers regularly met with the groups to discuss the questions

| Interview of the conduction of the conduction of the principal way and the principal | afox 🔻 📕 🖉 utt Curso: ARQUITECT. E ING. D | E COMP × 🗍 Green     | Web                           | × +                 |                           | _                           |             |   |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------|-------------------------------|---------------------|---------------------------|-----------------------------|-------------|---|---|

| Content: Which of the following statements about RISC Architectures is correct?         Answer time: 240         Correct answer: 3         Difficulty: 0.4         Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC Gehends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes <b>Course Name Nellot(clependency)</b><br><b>Arquitectura</b> Procesadores Segmentados 0.9 <u>View</u><br><b>La (1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | siena. <b>ull.es</b> /questions/31533     |                      |                               |                     |                           | ☆ マ C 🔮 - Swe               | etIM Search | م | Â |

| Answer time: 240         Correct answer: 3         Difficulty: 0.4         Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Relation(dependency)         Arquitectura       Procesadores Segmentados         0.9       View         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |                      |                               |                     |                           |                             |             |   |   |

| Answer time: 240         Correct answer: 3         Difficulty: 0.4         Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes <b>fourse</b> Name Relation(dependency)<br><b>Arquitectum</b> Procesadores Segmentades 0.9 View<br><b>11/1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                      |                               |                     |                           |                             |             |   |   |

| Answer time: 240         Correct answer: 3         Difficulty: 0.4         Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes <b>fourse</b> Name Relation(dependency)<br><b>Arquitectum</b> Procesadores Segmentades 0.9 View<br><b>11/1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                      |                               |                     |                           |                             |             |   |   |

| Answer time: 240         Correct answer: 3         Difficulty: 0.4         Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Arquitectura Procesadores Segmentados       0.9       Yiew         11/1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                           |                      |                               |                     |                           |                             |             |   |   |

| Answer time: 240<br>Correct answer: 3<br>Difficulty: 0.4<br>Luck: 0.25<br>Image:<br>Created by: grupo<br>Response list<br>The codes in RISC programs consist of fewer instructions than their CISC equivalents<br>The RISC philosophy is founded on the principle that in order to improve the computer 's performance it is necessary<br>to minimize the number of clock cycles needed to execute instructions<br>RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such,<br>makes execution times faster.<br>RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster<br>Associated nodes<br>Toruse Name Relation(dependency)<br>Arquitectura Procesadores Segmentados 0.9 View<br>1-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | Content: Which of t  | he following statements abo   | ut PISC Architect   | ires is correct?          |                             |             |   |   |

| Correct answer: 3 Difficulty: 0.4 Luck: 0.25 Image: Created by: grupo Response list The coles in RISC programs consist of fewer instructions than their CISC equivalents The RISC philosophy is founded on the principle that in order to improve the computer 's performance it is necessary to minimize the number of clock cycles needed to execute instructions RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster. RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster Associated nodes $ \hline Course & Name & Relation(dependency) \\ Arquitectura & Procesadores Segmentados & 0.9 & View \\ \hline 11/1 $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | content. which of    | ne ionowing statements abo    | at Ribe Architecte  | ites is correct:          |                             |             |   |   |

| Difficulty: 0.4<br>Luck: 0.25<br>Image:<br>Created by: grupo<br>Response list<br>The codes in RISC programs consist of fewer instructions than their CISC equivalents<br>The codes in RISC programs consist of fewer instructions than their CISC equivalents<br>The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary<br>to minimize the number of clock cycles needed to execute instructions<br>RISC Architecturie indicates that increasing the addressing modes allows data to be more easily accessed, and as such,<br>makes execution times faster.<br>RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster<br>Arquitectura Procesadores Segmentados 0.9 View<br>1-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           | Answer time: 240     |                               |                     |                           |                             |             |   |   |

| Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Yourse       Name         Arquitectura       Procesadores Segmentados         0.9       Yiew         1.1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           | Correct answer: 3    |                               |                     |                           |                             |             |   |   |

| Luck: 0.25         Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Arquitectura       Procesadores Segmentados         0.9 <u>View</u> 1.1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           | Diffemltru o d       |                               |                     |                           |                             |             |   |   |

| Image:         Created by: grupo         Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Relation(dependency)         Arquitectura       Procesadores Segmentados         0.9       View         1-1 / 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | Diffeurly: 0.4       |                               |                     |                           |                             |             |   |   |

| Created by: grupo         Response list         The coles in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Relation(dependency)         Arquitectura       Procesadores Segmentados         0.9 <u>View</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           | Luck: 0.25           |                               |                     |                           |                             |             |   |   |

| Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Arquitectura       Procesadores Segmentados         0.9 <u>View</u> 1       1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | Image:               |                               |                     |                           |                             |             |   |   |

| Response list         The codes in RISC programs consist of fewer instructions than their CISC equivalents         The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions         RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster.         RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster         Associated nodes         Course       Name         Relation(dependency)         Arquitectura       Procesadores Segmentados         0.9 <u>View</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                           | Created by: grupo    |                               |                     |                           |                             |             |   |   |

| The codes in RISC programs consist of fewer instructions than their CISC equivalents The RISC philosophy is founded on the principle that in order to improve the computer's performance it is necessary to minimize the number of clock cycles needed to execute instructions RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such, makes execution times faster. RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster Associated nodes           Course         Relation(dependency)           Arquitectura         Procesadores Segmentados         0.9         View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                      |                               |                     |                           |                             |             |   |   |

| to minimize the number of clock cycles needed to execute instructions<br>RISC Architecture indicates that increasing the addressing modes allows data to be more easily accessed, and as such,<br>makes execution times faster.<br>RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster<br>Associated nodes<br>Course Name Relation(dependency)<br>Arquitectura Procesadores Segmentados 0.9 View<br>1-1 / 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                      | rograms consist of fewer ins  | tructions than thei | r CISC equivalents        |                             |             |   |   |

| makes execution times faster.<br>RISC defends data dependences, in the pipeline processors these must be resolved by the hardware as it is faster<br>Associated nodes<br><u>Course Name Relation(dependency)</u><br>Arquitectura Procesadores Segmentados 0.9 <u>View</u><br><b>1</b> -1 / 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |                      |                               |                     |                           | rformance it is necessary   |             |   |   |

| Associated nodes     Name     Relation(dependency)       Arquitectura     Procesadores Segmentados     0.9     View       1-1 / 1     1-1 / 1     1-1 / 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           | RISC Architecture in | dicates that increasing the a |                     |                           | sily accessed, and as such, |             |   |   |

| Course     Name     Relation(dependency)       Arquitectura     Procesadores Segmentados     0.9     View       1-1/1     1-1/1     1-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           | RISC defends data d  | ependences, in the pipeline   | processors these m  | ust be resolved by the ha | rdware as it is faster      |             |   |   |

| Course     Name     Relation(dependency)       Arquitectura     Procesadores Segmentados     0.9     View       1-1 / 1     1-1     1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           | ·····                |                               |                     |                           |                             |             |   |   |

| Arquitectura Procesadores Segmentados o.9 <u>View</u><br>1-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |                      | Name                          | Relation(depo       | endency)                  |                             |             |   |   |

| 1-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | Arquitectura F       | rocesadores Segmentados       |                     |                           |                             |             |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           |                      |                               | ,                   |                           |                             |             |   |   |

| DACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           | Pauls                |                               |                     | 1-1 / 1                   |                             |             |   |   |